# Introduction to Parallel Processing

Algorithms and Architectures

Behrooz Parhami

### Introduction to Parallel Processing

Algorithms and Architectures

### PLENUM SERIES IN COMPUTER SCIENCE

Series Editor: Rami G. Melhem

University of Pittsburgh Pittsburgh, Pennsylvania

FUNDAMENTALS OF X PROGRAMMING Graphical User Interfaces and Beyond Theo Pavlidis

INTRODUCTION TO PARALLEL PROCESSING Algorithms and Architectures Behrooz Parhami

# Introduction to Parallel Processing Algorithms and Architectures

### Behrooz Parhami

University of California at Santa Barbara Santa Barbara, California

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN 0-306-46964-2 Print ISBN 0-306-45970-1

©2002 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://www.kluweronline.com and Kluwer's eBookstore at: http://www.ebooks.kluweronline.com

To the four parallel joys in my life,

for their love and support.

### **Preface**

### THE CONTEXT OF PARALLEL PROCESSING

The field of digital computer architecture has grown explosively in the past two decades. Through a steady stream of experimental research, tool-building efforts, and theoretical studies, the design of an instruction-set architecture, once considered an art, has been transformed into one of the most quantitative branches of computer technology. At the same time, better understanding of various forms of concurrency, from standard pipelining to massive parallelism, and invention of architectural structures to support a reasonably efficient and user-friendly programming model for such systems, has allowed hardware performance to continue its exponential growth. This trend is expected to continue in the near future.

This explosive growth, linked with the expectation that performance will continue its exponential rise with each new generation of hardware and that (in stark contrast to software) computer hardware will function correctly as soon as it comes off the assembly line, has its down side. It has led to unprecedented hardware complexity and almost intolerable development costs. The challenge facing current and future computer designers is to institute simplicity where we now have complexity; to use fundamental theories being developed in this area to gain performance and ease-of-use benefits from simpler circuits; to understand the interplay between technological capabilities and limitations, on the one hand, and design decisions based on user and application requirements on the other.

In computer designers' quest for user-friendliness, compactness, simplicity, high performance, low cost, and low power, parallel processing plays a key role. High-performance uniprocessors are becoming increasingly complex, expensive, and power-hungry. A basic trade-off thus exists between the use of one or a small number of such complex processors, at one extreme, and a moderate to very large number of simpler processors, at the other. When combined with a high-bandwidth, but logically simple, interprocessor communication facility, the latter approach leads to significant simplification of the design process. However, two major roadblocks have thus far prevented the widespread adoption of such moderately to massively parallel architectures: the interprocessor communication bottleneck and the difficulty, and thus high cost, of algorithm/software development.

The above context is changing because of several factors. First, at very high clock rates, the link between the processor and memory becomes very critical. CPUs can no longer be designed and verified in isolation. Rather, an integrated processor/memory design optimization is required, which makes the development even more complex and costly. VLSI technology now allows us to put more transistors on a chip than required by even the most advanced superscalar processor. The bulk of these transistors are now being used to provide additional on-chip memory. However, they can just as easily be used to build multiple processors on a single chip. Emergence of multiple-processor microchips, along with currently available methods for glueless combination of several chips into a larger system and maturing standards for parallel machine models, holds the promise for making parallel processing more practical.

This is the reason parallel processing occupies such a prominent place in computer architecture education and research. New parallel architectures appear with amazing regularity in technical publications, while older architectures are studied and analyzed in novel and insightful ways. The wealth of published theoretical and practical results on parallel architectures and algorithms is truly awe-inspiring. The emergence of standard programming and communication models has removed some of the concerns with compatibility and software design issues in parallel processing, thus resulting in new designs and products with mass-market appeal. Given the computation-intensive nature of many application areas (such as encryption, physical modeling, and multimedia), parallel processing will continue to thrive for years to come.

Perhaps, as parallel processing matures further, it will start to become invisible. Packing many processors in a computer might constitute as much a part of a future computer architect's toolbox as pipelining, cache memories, and multiple instruction issue do today. In this scenario, even though the multiplicity of processors will not affect the end user or even the professional programmer (other than of course boosting the system performance), the number might be mentioned in sales literature to lure customers in the same way that clock frequency and cache size are now used. The challenge will then shift from making parallel processing work to incorporating a larger number of processors, more economically and in a truly seamless fashion.

### THE GOALS AND STRUCTURE OF THIS BOOK

The field of parallel processing has matured to the point that scores of texts and reference books have been published. Some of these books that cover parallel processing in general (as opposed to some special aspects of the field or advanced/unconventional parallel systems) are listed at the end of this preface. Each of these books has its unique strengths and has contributed to the formation and fruition of the field. The current text, *Introduction to Parallel Processing: Algorithms and Architectures*, is an outgrowth of lecture notes that the author has developed and refined over many years, beginning in the mid-1980s. Here are the most important features of this text in comparison to the listed books:

Division of material into lecture-size chapters. In my approach to teaching, a lecture

is a more or less self-contained module with links to past lectures and pointers to

what will transpire in the future. Each lecture must have a theme or title and must

PREFACE ix

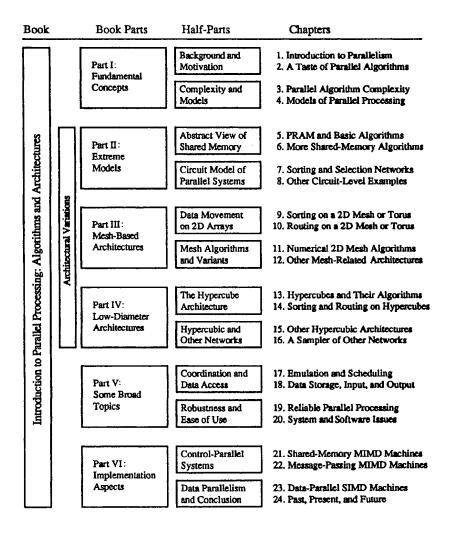

proceed from motivation, to details, to conclusion. There must be smooth transitions between lectures and a clear enunciation of how each lecture fits into the overall plan. In designing the text, I have strived to divide the material into chapters, each of which is suitable for one lecture (I–2 hours). A short lecture can cover the first few subsections, while a longer lecture might deal with more advanced material near the end. To make the structure hierarchical, as opposed to flat or linear, chapters have been grouped into six parts, each composed of four closely related chapters (see diagram on page xi).

- 2. A large number of meaningful problems. At least 13 problems have been provided at the end of each of the 24 chapters. These are well-thought-out problems, many of them class-tested, that complement the material in the chapter, introduce new viewing angles, and link the chapter material to topics in other chapters.

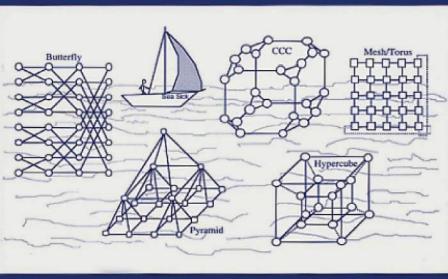

- 3. Emphasis on both the underlying theory and practical designs. The ability to cope with complexity requires both a deep knowledge of the theoretical underpinnings of parallel processing and examples of designs that help us understand the theory. Such designs also provide hints/ideas for synthesis as well as reference points for cost–performance comparisons. This viewpoint is reflected, e.g., in the coverage of problem-driven parallel machine designs (Chapter 8) that point to the origins of the butterfly and binary-tree architectures. Other examples are found in Chapter 16 where a variety of composite and hierarchical architectures are discussed and some fundamental cost–performance trade-offs in network design are exposed. Fifteen carefully chosen case studies in Chapters 21–23 provide additional insight and motivation for the theories discussed.

- 4. Linking parallel computing to other subfields of computer design. Parallel computing is nourished by, and in turn feeds, other subfields of computer architecture and technology. Examples of such links abound. In computer arithmetic, the design of high-speed adders and multipliers contributes to, and borrows many methods from, parallel processing. Some of the earliest parallel systems were designed by researchers in the field of fault-tolerant computing in order to allow independent multichannel computations and/or dynamic replacement of failed subsystems. These links are pointed out throughout the book.

- 5. Wide coverage of important topics. The current text covers virtually all important architectural and algorithmic topics in parallel processing, thus offering a balanced and complete view of the field. Coverage of the circuit model and problem-driven parallel machines (Chapters 7 and 8), some variants of mesh architectures (Chapter 12), composite and hierarchical systems (Chapter 16), which are becoming increasingly important for overcoming VLSI layout and packaging constraints, and the topics in Part V (Chapters 17–20) do not all appear in other textbooks. Similarly, other books that cover the foundations of parallel processing do not contain discussions on practical implementation issues and case studies of the type found in Part VI.

- 6. Unified and consistent notation/terminology throughout the text. I have tried very hard to use consistent notation/terminology throughout the text. For example, *n* always stands for the number of data elements (problem size) and *p* for the number of processors. While other authors have done this in the basic parts of their texts, there is a tendency to cover more advanced research topics by simply borrowing

the notation and terminology from the reference source. Such an approach has the advantage of making the transition between reading the text and the original reference source easier, but it is utterly confusing to the majority of the students who rely on the text and do not consult the original references except, perhaps, to write a research paper.

### SUMMARY OF TOPICS

The six parts of this book, each composed of four chapters, have been written with the following goals:

- Part I sets the stage, gives a taste of what is to come, and provides the needed perspective, taxonomy, and analysis tools for the rest of the book.

- Part II delimits the models of parallel processing from above (the abstract PRAM model) and from below (the concrete circuit model), preparing the reader for everything else that falls in the middle.

- Part III presents the scalable, and conceptually simple, mesh model of parallel processing, which has become quite important in recent years, and also covers some of its derivatives.

- Part IV covers low-diameter parallel architectures and their algorithms, including the hypercube, hypercube derivatives, and a host of other interesting interconnection topologies.

- Part V includes broad (architecture-independent) topics that are relevant to a wide range

of systems and form the stepping stones to effective and reliable parallel processing.

- Part VI deals with implementation aspects and properties of various classes of parallel

processors, presenting many case studies and projecting a view of the past and future

of the field.

### POINTERS ON HOW TO USE THE BOOK

For classroom use, the topics in each chapter of this text can be covered in a lecture spanning 1–2 hours. In my own teaching, I have used the chapters primarily for 1-1/2-hour lectures, twice a week, in a 10-week quarter, omitting or combining some chapters to fit the material into 18–20 lectures. But the modular structure of the text lends itself to other lecture formats, self-study, or review of the field by practitioners. In the latter two cases, the readers can view each chapter as a study unit (for 1 week, say) rather than as a lecture. Ideally, all topics in each chapter should be covered before moving to the next chapter. However, if fewer lecture hours are available, then some of the subsections located at the end of chapters can be omitted or introduced only in terms of motivations and key results.

Problems of varying complexities, from straightforward numerical examples or exercises to more demanding studies or miniprojects, have been supplied for each chapter. These problems form an integral part of the book and have not been added as afterthoughts to make the book more attractive for use as a text. A total of 358 problems are included (13–16 per chapter). Assuming that two lectures are given per week, either weekly or biweekly homework can be assigned, with each assignment having the specific coverage of the respective half-part

PREFACE X İ

The structure of this book in parts, half-parts, and chapters.

(two chapters) or full part (four chapters) as its "title." In this format, the half-parts, shown above, provide a focus for the weekly lecture and/or homework schedule.

An instructor's manual, with problem solutions and enlarged versions of the diagrams and tables, suitable for reproduction as transparencies, is planned. The author's detailed syllabus for the course ECE 254B at UCSB is available at http://www.ece.ucsb.edu/courses/syllabi/ece254b.html.

References to important or state-of-the-art research contributions and designs are provided at the end of each chapter. These references provide good starting points for doing in-depth studies or for preparing term papers/projects.

New ideas in the field of parallel processing appear in papers presented at several annual conferences, known as FMPC, ICPP, IPPS, SPAA, SPDP (now merged with IPPS), and in archival journals such as *IEEE Transactions on Computers* [TCom], *IEEE Transactions on Parallel and Distributed Systems* [TPDS], *Journal of Parallel and Distributed Computing* [JPDC], *Parallel Computing* [ParC], and *Parallel Processing Letters* [PPL]. Tutorial and survey papers of wide scope appear in *IEEE Concurrency* [Conc] and, occasionally, in *IEEE Computer* [Comp]. The articles in *IEEE Computer* provide excellent starting points for research projects and term papers.

### **ACKNOWLEDGMENTS**

The current text, *Introduction to Parallel Processing: Algorithms and Architectures*, is an outgrowth of lecture notes that the author has used for the graduate course "ECE 254B: Advanced Computer Architecture: Parallel Processing" at the University of California, Santa Barbara, and, in rudimentary forms, at several other institutions prior to 1988. The text has benefited greatly from keen observations, curiosity, and encouragement of my many students in these courses. A sincere thanks to all of them! Particular thanks go to Dr. Ding-Ming Kwai who read an early version of the manuscript carefully and suggested numerous corrections and improvements.

### **GENERAL REFERENCES**

[Akl89] Akl, S. G., The Design and Analysis of Parallel Algorithms, Prentice-Hall, 1989.

[Akl97] Akl, S. G., Parallel Computation: Models and Methods, Prentice-Hall, 1997.

[Alma94] Almasi, G. S., and A. Gottlieb, Highly Parallel Computing, Benjamin/Cummings, 2nd ed., 1994.

[Bert89] Bertsekas, D. P., and J. N. Tsitsiklis, Parallel and Distributed Computation: Numerical Methods, Prentice—Hall, 1989.

[Code93] Codenotti, B., and M. Leoncini, Introduction to Parallel Processing, Addison-Wesley, 1993.

[Comp] IEEE Computer, journal published by IEEE Computer Society: has occasional special issues on parallel/distributed processing (February 1982, June 1985, August 1986, June 1987, March 1988, August 1991, February 1992, November 1994, November 1995, December 1996).

[Conc] IEEE Concurrency, formerly IEEE Parallel and Distributed Technology, magazine published by IEEE Computer Society.

[Cric88] Crichlow, J. M., Introduction to Distributed and Parallel Computing, Prentice-Hall, 1988.

[DeCe89] DeCegama, A. L., Parallel Processing Architectures and VLSI Hardware, Prentice-Hall, 1989.

[Desr87] Desrochers, G. R., Principles of Parallel and Multiprocessing, McGraw-Hill, 1987.

[Duat97] Duato, J., S. Yalamanchili, and L. Ni, Interconnection Networks: An Engineering Approach, IEEE Computer Society Press, 1997.

[Flyn95] Flynn, M. J., Computer Architecture: Pipelined and Parallel Processor Design, Jones and Bartlett, 1995.

[FMPC] Proc. Symp. Frontiers of Massively Parallel Computation, sponsored by IEEE Computer Society and NASA. Held every 1 1/2–2 years since 1986. The 6th FMPC was held in Annapolis, MD, October 27–31, 1996, and the 7th is planned for February 20–25, 1999.

[Foun94] Fountain, T. J., Parallel Computing: Principles and Practice, Cambridge University Press, 1994.

[Hock81] Hockney, R. W., and C. R. Jesshope, Parallel Computers, Adam Hilger, 1981.

[Hord90] Hord, R. M., Parallel Supercomputing in SIMD Architectures, CRC Press, 1990.

[Hord93] Hord, R. M., Parallel Supercomputing in MIMD Architectures, CRC Press, 1993.

[Hwan84] Hwang, K., and F. A. Briggs, Computer Architecture and Parallel Processing, McGraw-Hill, 1984.

[Hwan93] Hwang, K., Advanced Computer Architecture: Parallelism, Scalability, Programmability, McGraw-Hill, 1993.

PREFACE XIII

[Hwan98] Hwang, K., and Z. Xu, Scalable Parallel Computing: Technology, Architecture, Programming, McGraw-Hill, 1998.

- [ICPP] Proc. Int. Conference Parallel Processing, sponsored by The Ohio State University (and in recent years, also by the International Association for Computers and Communications). Held annually since 1972.

- [IPPS] Proc. Int. Parallel Processing Symp., sponsored by IEEE Computer Society. Held annually since 1987. The 11th IPPS was held in Geneva, Switzerland, April 1–5, 1997. Beginning with the 1998 symposium in Orlando, FL, March 30–April 3, IPPS was merged with SPDP. \*\*

- [JaJa92] JaJa, J., An Introduction to Parallel Algorithms, Addison-Wesley, 1992.

- [JPDC] Journal of Parallel and Distributed Computing, Published by Academic Press.

- [Kris89] Krishnamurthy, E. V., Parallel Processing: Principles and Practice, Addison-Wesley, 1989.

- [Kuma94] Kumar, V., A. Grama, A. Gupta, and G. Karypis, Introduction to Parallel Computing: Design and Analysis of Algorithms, Benjamin/Cummings, 1994.

- [Laks90] Lakshmivarahan, S., and S. K. Dhall, Analysis and Design of Parallel Algorithms: Arithmetic and Matrix Problems, McGraw-Hill, 1990.

- [Leig92] Leighton, F. T., Introduction to Parallel Algorithms and Architectures: Arrays, Trees, Hypercubes, Morgan Kaufmann, 1992.

- [Lerm94] Lerman, G., and L. Rudolph, Parallel Evolution of Parallel Processors, Plenum, 1994.

- [Lipo87] Lipovski, G. J., and M. Malek, Parallel Computing: Theory and Comparisons, Wiley, 1987.

- [Mold93] Moldovan, D. I., Parallel Processing: From Applications to Systems, Morgan Kaufmann, 1993.

- [ParC] Parallel Computing, journal published by North-Holland.

- [PPL] Parallel Processing Letters, journal published by World Scientific.

- [Quin87] Quinn, M. J., Designing Efficient Algorithms for Parallel Computers, McGraw-Hill, 1987.

- [Quin94] Quinn, M. J., Parallel Computing: Theory and Practice, McGraw-Hill, 1994.

- [Reif93] Reif, J. H. (ed.), Synthesis of Parallel Algorithms, Morgan Kaufmann, 1993.

- [Sanz 89] Sanz, J. L. C. (ed.), Opportunities and Constraints of Parallel Computing (IBM/NSF Workshop, San Jose, CA, December 1988), Springer-Verlag, 1989.

- [Shar87] Sharp, J. A., An Introduction to Distributed and Parallel Processing, Blackwell Scientific Publications, 1987.

- [Sieg85] Siegel, H. J., Interconnection Networks for Large-Scale Parallel Processing, Lexington Books, 1985.

- [SPAA] Proc. Symp. Parallel Algorithms and Architectures, sponsored by the Association for Computing Machinery (ACM). Held annually since 1989. The 10th SPAA was held in Puerto Vallarta, Mexico, June 28–July 2, 1998.

- [SPDP] Proc. Int. Symp. Parallel and Distributed Systems, sponsored by IEEE Computer Society. Held annually since 1989, except for 1997. The 8th SPDP was held in New Orleans, LA, October 23–26, 1996. Beginning with the 1998 symposium in Orlando, FL, March 30–April 3, SPDP was merged with IPPS.

- [Ston93] Stone, H. S., High-Performance Computer Architecture, Addison-Wesley, 1993.

- [TCom] IEEE Trans. Computers, journal published by IEEE Computer Society; has occasional special issues on parallel and distributed processing (April 1987, December 1988, August 1989, December 1991, April 1997, April 1998).

- [TPDS] IEEE Trans. Parallel and Distributed Systems, journal published by IEEE Computer Society.

- [Varm94] Varma, A., and C. S. Raghavendra, Interconnection Networks for Multiprocessors and Multicomputers: Theory and Practice, IEEE Computer Society Press, 1994.

- [Zoma96] Zomaya, A. Y. (ed.), Parallel and Distributed Computing Handbook, McGraw-Hill, 1996.

<sup>\*</sup>The 27th ICPP was held in Minneapolis, MN, August 10–15, 1998, and the 28th is scheduled for September 21–24, 1999, in Aizu, Japan.

<sup>\*\*</sup>The next joint IPPS/SPDP is sceduled for April 12–16, 1999, in San Juan, Puerto Rico.

### Contents

| Funda | mental Concepts                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intro | duction to Parallelism                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1.  | Why Parallel Processing?                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2.  | A Motivating Example                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3.  | Parallel Processing Ups and Downs                                                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4.  | Types of Parallelism: A Taxonomy                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.5.  | Roadblocks to Parallel Processing                                                                                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.6.  | Effectiveness of Parallel Processing                                                                                       | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Prob  |                                                                                                                            | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Refe  | rences and Suggested Reading                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A Ta  | ste of Parallel Algorithms                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

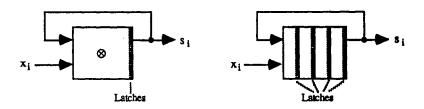

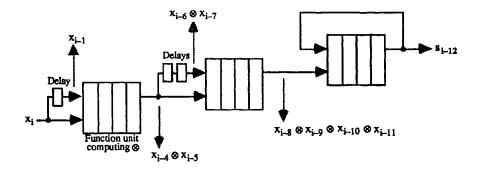

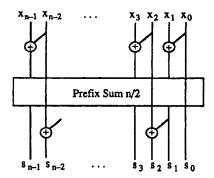

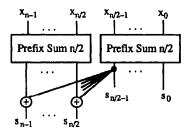

| 2.1.  | Some Simple Computations                                                                                                   | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

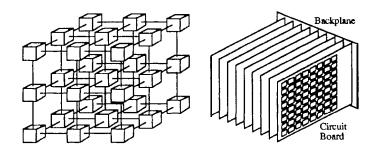

| 2.2.  | Some Simple Architectures                                                                                                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3.  |                                                                                                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4.  |                                                                                                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.5.  |                                                                                                                            | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.6.  |                                                                                                                            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Proh  |                                                                                                                            | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                            | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

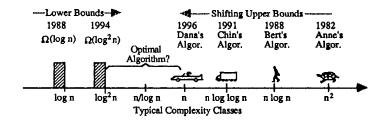

| Para  | ıllel Algorithm Complexity                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1.  | Asymptotic Complexity                                                                                                      | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2.  | Algorithm Optimality and Efficiency                                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

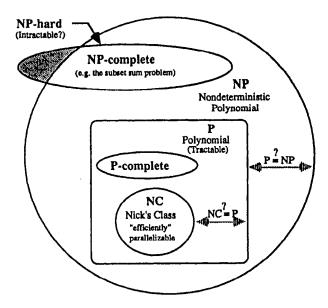

| 3.3.  |                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.4.  |                                                                                                                            | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.5.  |                                                                                                                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.6.  | Solving Recurrences                                                                                                        | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | Intro 1.1. 1.2. 1.3. 1.4. 1.5. 1.6. Prob Refe  A Ta 2.1. 2.2. 2.3. 2.4. 2.5. 2.6. Prob Refe  Para 3.1. 3.2. 3.3. 3.4. 3.5. | 1.2. A Motivating Example 1.3. Parallel Processing Ups and Downs 1.4. Types of Parallelism: A Taxonomy 1.5. Roadblocks to Parallel Processing 1.6. Effectiveness of Parallel Processing Problems References and Suggested Reading  A Taste of Parallel Algorithms  2.1. Some Simple Computations 2.2. Some Simple Architectures 2.3. Algorithms for a Linear Array 2.4. Algorithms for a Binary Tree 2.5. Algorithms for a 2D Mesh 2.6. Algorithms with Shared Variables Problems References and Suggested Reading  Parallel Algorithm Complexity 3.1. Asymptotic Complexity 3.2. Algorithm Optimality and Efficiency 3.3. Complexity Classes 3.4. Parallelizable Tasks and the NC Class 3.5. Parallel Programming Paradigms |

|            | Problems                                                                                                                                                                                                                                                                     |                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

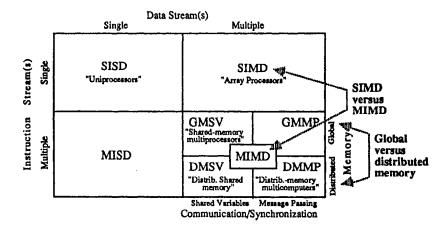

| 4.         | Models of Parallel Processing                                                                                                                                                                                                                                                | 5                          |

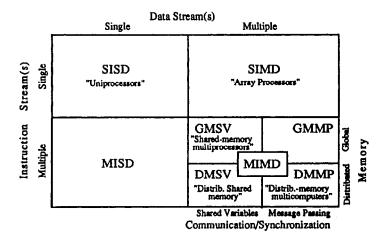

|            | 4.1. Development of Early Models64.2. SIMD versus MIMD Architectures64.3. Global versus Distributed Memory74.4. The PRAM Shared-Memory Model74.5. Distributed-Memory or Graph Models74.6. Circuit Model and Physical Realizations8Problems8References and Suggested Reading8 | 9<br>1<br>4<br>7<br>0<br>2 |

| Part II. E | Extreme Models                                                                                                                                                                                                                                                               | 7                          |

| 5.         | PRAM and Basic Algorithms                                                                                                                                                                                                                                                    | 9                          |

|            | 5.1. PRAM Submodels and Assumptions95.2. Data Broadcasting95.3. Semigroup or Fan-In Computation95.4. Parallel Prefix Computation95.5. Ranking the Elements of a Linked List95.6. Matrix Multiplication10Problems10References and Suggested Reading10                         | 3<br>6<br>8<br>9<br>2<br>5 |

| 6.         | More Shared-Memory Algorithms                                                                                                                                                                                                                                                | 9                          |

|            | 6.1. Sequential Rank-Based Selection116.2. A Parallel Selection Algorithm116.3. A Selection-Based Sorting Algorithm116.4. Alternative Sorting Algorithms116.5. Convex Hull of a 2D Point Set116.6. Some Implementation Aspects12Problems12References and Suggested Reading12 | 3<br>4<br>7<br>8<br>1      |

| 7.         | Sorting and Selection Networks                                                                                                                                                                                                                                               | 9                          |

|            | 7.1. What Is a Sorting Network137.2. Figures of Merit for Sorting Networks137.3. Design of Sorting Networks137.4. Batcher Sorting Networks137.5. Other Classes of Sorting Networks147.6. Selection Networks14Problems14References and Suggested Reading14                    | 3<br>6<br>1<br>2           |

CONTENTS xvii

| 8.        | Other Circuit-Level Examples                                                                                                                                                                                                                                 | 149                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|           | 8.1. Searching and Dictionary Operations                                                                                                                                                                                                                     | 151<br>152<br>156<br>157<br>161<br>163<br>165             |

| Part III. | Mesh-Based Architectures · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                               | 169                                                       |

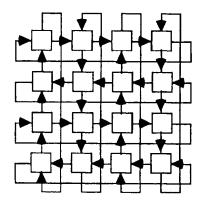

| 9.        | Sorting on a 2D Mesh or Torus                                                                                                                                                                                                                                | 171                                                       |

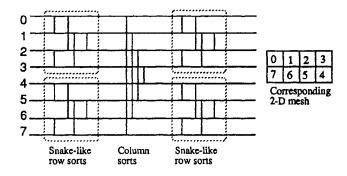

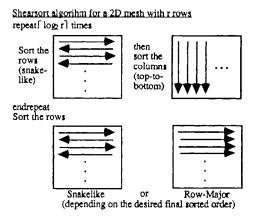

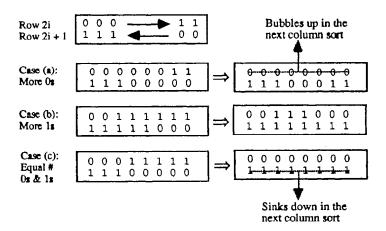

|           | 9.1. Mesh-Connected Computers 9.2. The Shearsort Algorithm 9.3. Variants of Simple Shearsort 9.4. Recursive Sorting Algorithms 9.5. A Nontrivial Lower Bound 9.6. Achieving the Lower Bound Problems References and Suggested Reading                        | 173<br>176<br>179<br>180<br>183<br>186<br>187             |

| 10.       | Routing on a 2D Mesh or Torus                                                                                                                                                                                                                                | 191                                                       |

|           | 10.1. Types of Data Routing Operations  10.2. Useful Elementary Operations  10.3. Data Routing on a 2D Array  10.4. Greedy Routing Algorithms  10.5. Other Classes of Routing Algorithms  10.6. Wormhole Routing  Problems  References and Suggested Reading | 193<br>195<br>197<br>199<br>202<br>204<br>208<br>210      |

| 11.       | Numerical 2D Mesh Algorithms                                                                                                                                                                                                                                 | 211<br>213<br>215<br>218<br>221                           |

|           | 11.5. Graph Algorithms                                                                                                                                                                                                                                       | <ul><li>225</li><li>228</li><li>231</li><li>233</li></ul> |

| 12.       | Other Mesh-Related Architectures                                                                                                                                                                                                                             | 235                                                       |

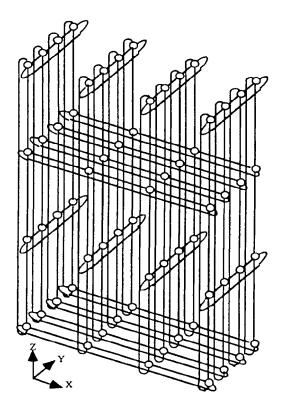

|           | 12.1 Three or More Dimensions                                                                                                                                                                                                                                | 237                                                       |

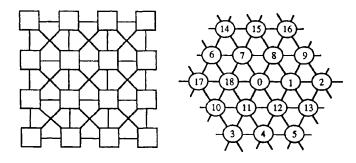

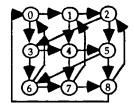

| 12.2. Stronger and Weaker Connectivities   | 240 |

|--------------------------------------------|-----|

| 12.3. Meshes Augmented with Nonlocal Links | 242 |

| 12.4. Meshes with Dynamic Links            | 245 |

| 12.5. Pyramid and Multigrid Systems        | 246 |

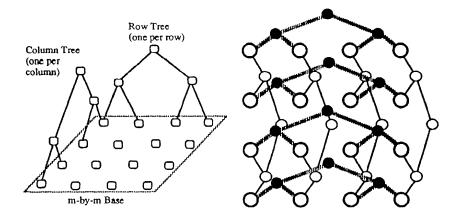

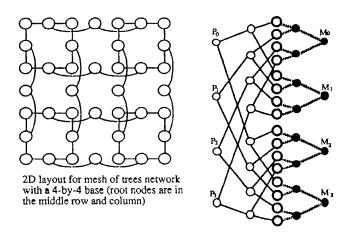

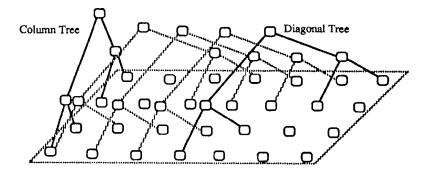

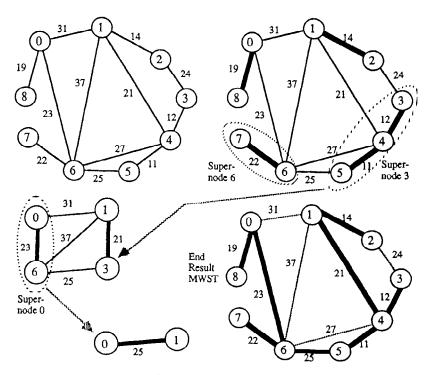

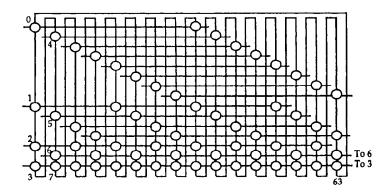

| 12.6. Meshes of Trees                      | 248 |

| Problems                                   | 253 |

| References and Suggested Reading           | 256 |

| Part IV. Low-Diameter Architectures        | 257 |

| 13. Hypercubes and Their Algorithms        | 259 |

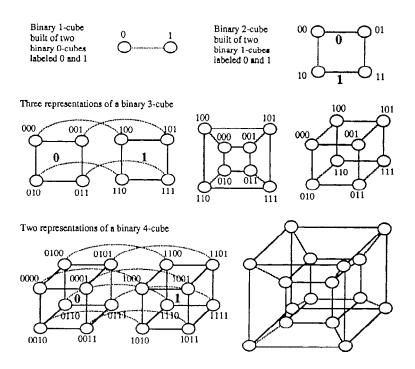

| 13.1. Definition and Main Properties       | 261 |

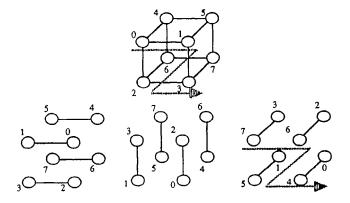

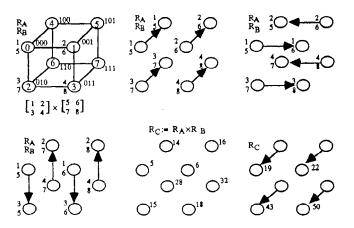

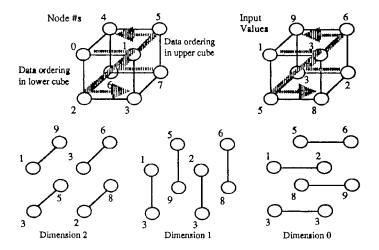

| 13.2. Embeddings and Their Usefulness      | 263 |

| 13.3. Embedding of Arrays and Trees        | 264 |

| 13.4. A Few Simple Algorithms              | 269 |

| 13.5. Matrix Multiplication                | 272 |

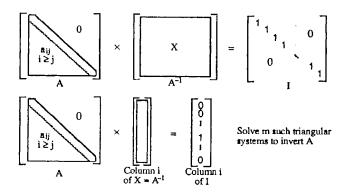

| 13.6. Inverting a Lower Triangular Matrix  | 274 |

| Problems                                   | 275 |

| References and Suggested Reading           | 278 |

| 14. Sorting and Routing on Hypercubes      | 279 |

| 14.1. Defining the Sorting Problem         | 281 |

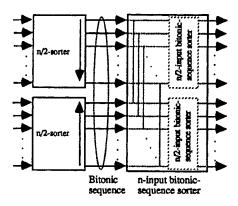

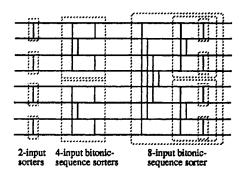

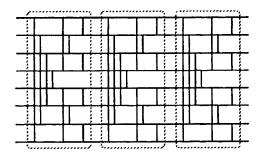

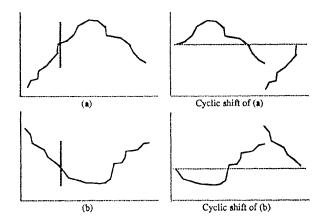

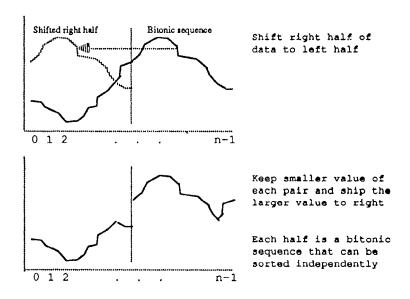

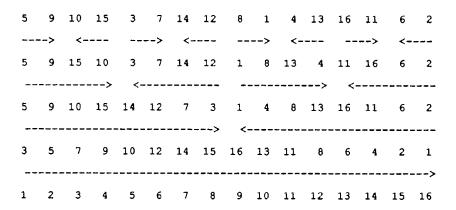

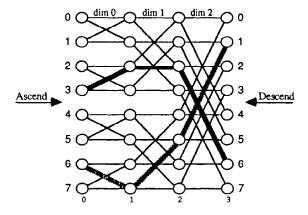

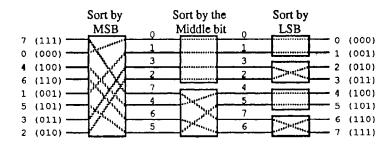

| 14.2. Bitonic Sorting on a Hypercube       | 284 |

| 14.3. Routing Problems on a Hypercube      | 285 |

| 14.4. Dimension-Order Routing              | 288 |

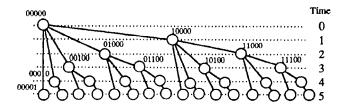

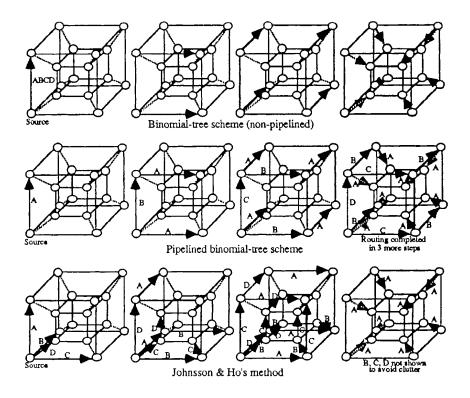

| 14.5. Broadcasting on a Hypercube          | 292 |

| 14.6. Adaptive and Fault-Tolerant Routing  | 294 |

| Problems                                   | 295 |

| References and Suggested Reading           | 298 |

| 45. Other Heavy Lie Auditories             |     |

| 15. Other Hypercubic Architectures         | 301 |

| 15.1. Modified and Generalized Hypercubes  | 303 |

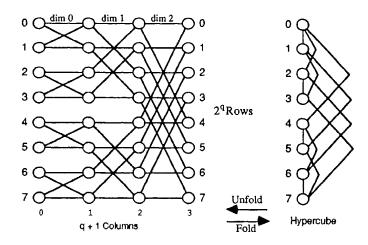

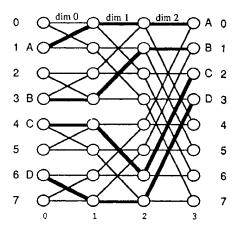

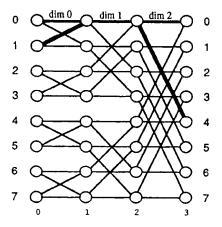

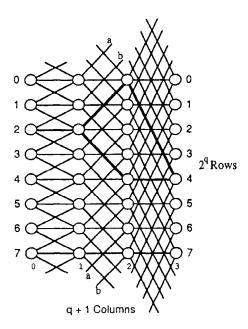

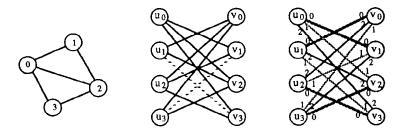

| 15.2. Butterfly and Permutation Networks   | 305 |

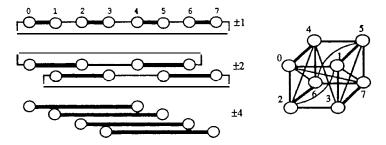

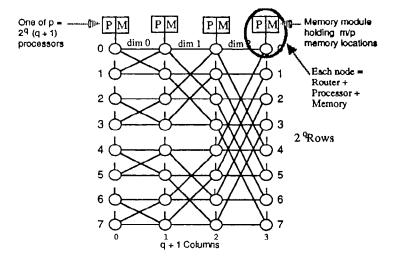

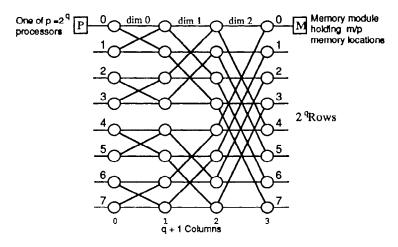

| 15.3. Plus-or-Minus-2'Network              | 309 |

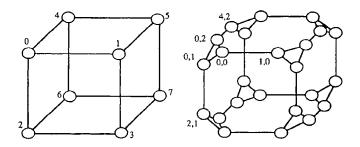

| 15.4. The Cube-Connected Cycles Network    | 310 |

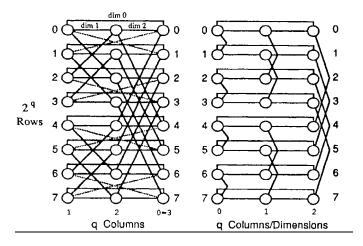

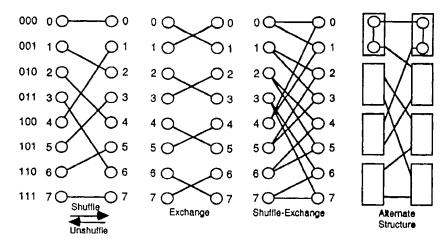

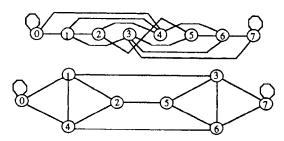

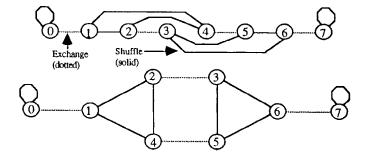

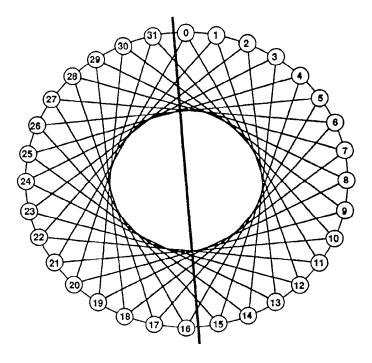

| 15.5. Shuffleand Shuffle–Exchange Networks | 313 |

| 15.6. That's Not All, Folks!               | 316 |

| Problems                                   | 317 |

| References and Suggested Reading           | 320 |

| 16. A Sampler of Other Networks            | 321 |

| 16.1. Performance Parameters for Networks  | 323 |

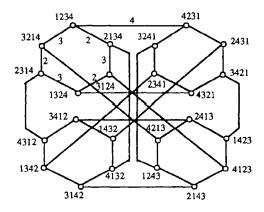

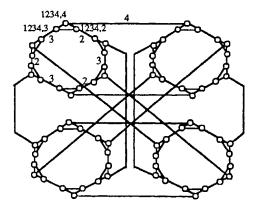

| 16.2. Star and Pancake Networks            | 326 |

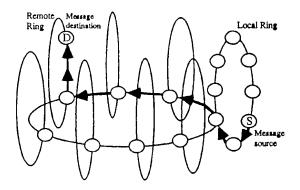

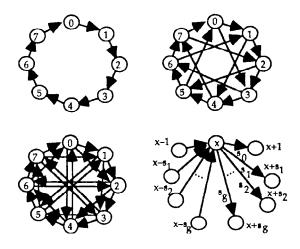

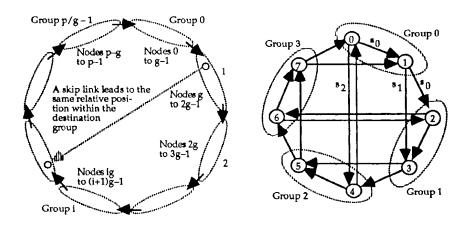

| 16.3. Ring-Based Networks                  | 329 |

CONTENTS XiX

|            | 16.4. Composite or Hybrid Networks                                                                                                                                                                                                                                        | 335<br>337<br>338<br>340<br>343                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Part V. So | ome Broad Topics                                                                                                                                                                                                                                                          | 345                                                  |

| 17.        | Emulation and Scheduling                                                                                                                                                                                                                                                  | 347                                                  |

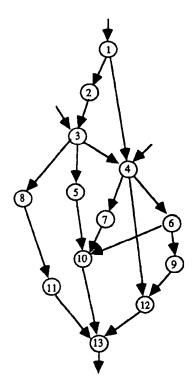

|            | 17.1. Emulations among Architectures 17.2. Distributed Shared Memory 17.3. The Task Scheduling Problem 17.4. A Class of Scheduling Algorithms 17.5. Some Useful Bounds for Scheduling 17.6. Load Balancing and Dataflow Systems Problems References and Suggested Reading | 349<br>351<br>355<br>357<br>360<br>362<br>364<br>367 |

| 18.        | Data Storage, Input, and Output                                                                                                                                                                                                                                           | 369                                                  |

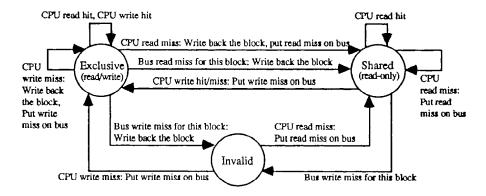

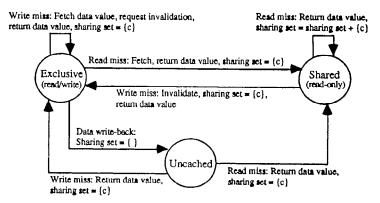

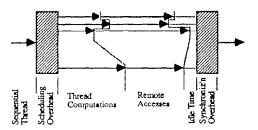

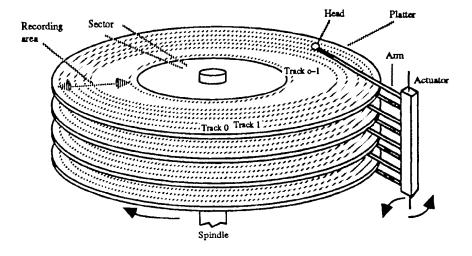

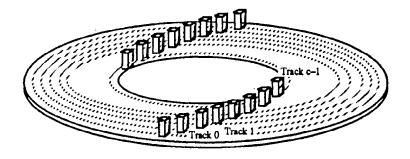

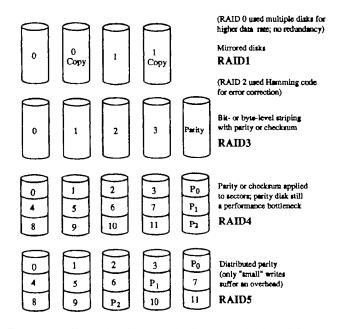

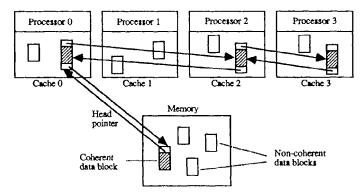

|            | 18.1. Data Access Problems and Caching 18.2. Cache Coherence Protocols 18.3. Multithreading and Latency Hiding 18.4. Parallel I/O Technology 18.5. Redundant Disk Arrays 18.6. Interfaces and Standards Problems References and Suggested Reading                         | 371<br>374<br>377<br>379<br>382<br>384<br>386<br>388 |

| 19.        | Reliable Parallel Processing                                                                                                                                                                                                                                              | 391                                                  |

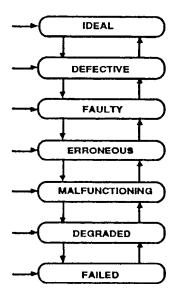

|            | 19.1. Defects, Faults, , Failures  19.2. Defect-Level Methods  19.3. Fault-Level Methods  19.4. Error-Level Methods  19.5. Malfunction-Level Methods  19.6. Degradation-Level Methods  Problems  References and Suggested Reading                                         | 393<br>396<br>399<br>402<br>404<br>407<br>410<br>413 |

| 20.        | System and Software Issues                                                                                                                                                                                                                                                | 415                                                  |

|            | 20.1. Coordination and Synchronization 20.2. Parallel Programming 20.3. Software Portability and Standards 20.4. Parallel Operating Systems 20.5. Parallel File Systems                                                                                                   | 417<br>421<br>425<br>427<br>430                      |

| F                          | 20.6. Hardware/Software Interaction                                                                                                                                                                                                                                          | 431<br>433<br>435                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                            |                                                                                                                                                                                                                                                                              |                                                      |

| Part VI. I                 | Implementation Aspects                                                                                                                                                                                                                                                       | 437                                                  |

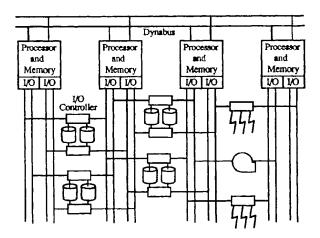

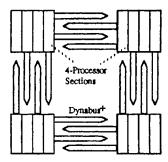

| 21.5                       | Shared-Memory MIMD Machines                                                                                                                                                                                                                                                  | 439                                                  |

| 2<br>2<br>2<br>2<br>2<br>F | 21.1. Variations in Shared Memory 21.2. MIN-Based BBN Butterfly 21.3. Vector-Parallel Cray Y-MP 21.4. Latency-Tolerant Tera MTA 21.5. CC-NUMA Stanford DASH 21.6. SCI-Based Sequent NUMA-Q Problems References and Suggested Reading                                         | 441<br>444<br>445<br>448<br>450<br>452<br>455<br>457 |

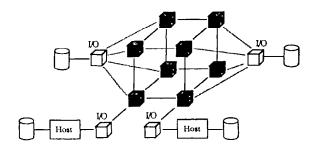

| 22. N                      | Message-Passing MIMD Machines                                                                                                                                                                                                                                                | 459                                                  |

| 2<br>2<br>2<br>2<br>2<br>F | 22.1. Mechanisms for Message Passing  22.2. Reliable Bus-Based Tandem Nonstop  22.3. Hypercube-Based nCUBE3  22.4. Fat-Tree-Based Connection Machine 5  22.5. Omega-Network-Based IBM SP2  22.6. Commodity-Driven Berkeley NOW  Problems  References and Suggested Reading   | 461<br>464<br>466<br>469<br>471<br>473<br>475        |

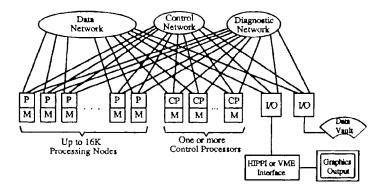

| 23. [                      | Data-Parallel SIMD Machines                                                                                                                                                                                                                                                  | 479                                                  |

| 2<br>2<br>2<br>2<br>2<br>F | 23.1. Where Have All the SIMDs Gone? 23.2. The First Supercomputer: ILLIAC IV 23.3. Massively Parallel Goodyear MPP 23.4. Distributed Array Processor (DAP) 23.5. Hypercubic Connection Machine 2 23.6. Multiconnected MasPar MP-2 Problems References and Suggested Reading | 481<br>484<br>485<br>488<br>490<br>492<br>495<br>497 |

| 24. F                      | Past, Present, and Future                                                                                                                                                                                                                                                    | 499                                                  |

| 2<br>2<br>2                | 24.1. Milestones in Parallel Processing                                                                                                                                                                                                                                      | 501<br>503<br>506<br>508<br>510                      |

| CONTENTS | xxi |

|----------|-----|

| CONTENTS | XX  |

| 24.6. The Future of Parallel Processing | 513 |

|-----------------------------------------|-----|

| Problems                                |     |

| References and Suggested Reading        | 517 |

| Index                                   | 519 |

### Introduction to Parallel Processing

Algorithms and Architectures

## Fundamental Concepts

The field of parallel processing is concerned with architectural and algorithmic methods for enhancing the performance or other attributes (e.g., cost-effectiveness, reliability) of digital computers through various forms of concurrency. Even though concurrent computation has been around since the early days of digital computers, only recently has it been applied in a manner, and on a scale, that leads to better performance, or greater cost-effectiveness, compared with vector supercomputers. Like any other field of science/technology, the study of parallel architectures and algorithms requires motivation, a big picture showing the relationships between problems and the various approaches to solving them, and models for comparing, connecting, and evaluating new ideas. This part, which motivates us to study parallel processing, paints the big picture, and provides some needed background, is composed of four chapters:

- Chapter 1: Introduction to Parallelism

- Chapter 2: A Taste of Parallel Algorithms

- Chapter 3: Parallel Algorithm Complexity

- Chapter 4: Models of Parallel Processing

### Introduction to Parallelism

This chapter sets the context in which the material in the rest of the book will be presented and reviews some of the challenges facing the designers and users of parallel computers. The chapter ends with the introduction of useful metrics for evaluating the effectiveness of parallel systems. Chapter topics are

- 1.1. Why parallel processing?

- 1.2. A motivating example

- 1.3. Parallel processing ups and downs

- 1.4. Types of parallelism: A taxonomy

- 1.5. Roadblocks to parallel processing

- 1.6. Effectiveness of parallel processing

### 1.1. WHY PARALLEL PROCESSING?

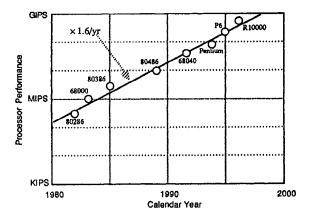

The quest for higher-performance digital computers seems unending. In the past two decades, the performance of microprocessors has enjoyed an exponential growth. The growth of microprocessor speed/performance by a factor of 2 every 18 months (or about 60% per year) is known as Moore's law. This growth is the result of a combination of two factors:

- Increase in complexity (related both to higher device density and to larger size) of VLSI chips, projected to rise to around 10 M transistors per chip for microprocessors, and 1B for dynamic random-access memories (DRAMs), by the year 2000 [SIA94]

- Introduction of, and improvements in, architectural features such as on-chip cache memories, large instruction buffers, multiple instruction issue per cycle, multithreading, deep pipelines, out-of-order instruction execution, and branch prediction

Moore's law was originally formulated in 1965 in terms of the doubling of chip complexity every year (later revised to every 18 months) based only on a small number of data points [Scha97]. Moore's revised prediction matches almost perfectly the actual increases in the number of transistors in DRAM and microprocessor chips.

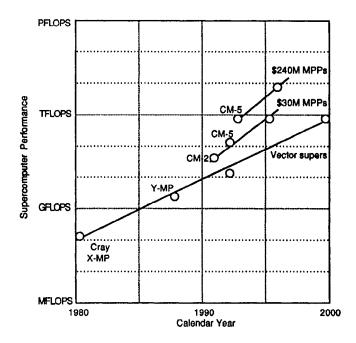

Moore's law seems to hold regardless of how one measures processor performance: counting the number of executed instructions per second (IPS), counting the number of floating-point operations per second (FLOPS), or using sophisticated benchmark suites that attempt to measure the processor's performance on real applications. This is because all of these measures, though numerically different, tend to rise at roughly the same rate. Figure 1.1 shows that the performance of actual processors has in fact followed Moore's law quite closely since 1980 and is on the verge of reaching the GIPS (giga IPS =  $10^9$  IPS) milestone.

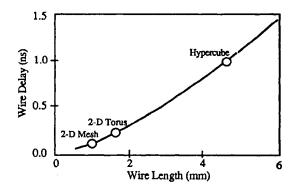

Even though it is expected that Moore's law will continue to hold for the near future, there is a limit that will eventually be reached. That some previous predictions about when the limit will be reached have proven wrong does not alter the fact that a limit, dictated by physical laws, does exist. The most easily understood physical limit is that imposed by the finite speed of signal propagation along a wire. This is sometimes referred to as the speed-of-light argument (or limit), explained as follows.

The Speed-of-Light Argument. The speed of light is about 30 cm/ns. Signals travel on a wire at a fraction of the speed of light. If the chip diameter is 3 cm, say, any computation that involves signal transmission from one end of the chip to another cannot be executed faster than 10<sup>10</sup> times per second. Reducing distances by a factor of 10 or even 100 will only increase the limit by these factors; we still cannot go beyond 10<sup>12</sup> computations per second. To relate the above limit to the instruction execution rate (MIPS or FLOPS), we need to estimate the distance that signals *must* travel within an instruction cycle. This is not easy to do, given the extensive use of pipelining and memory-latency-hiding techniques in modern high-performance processors. Despite this difficulty, it should be clear that we are in fact not very far from limits imposed by the speed of signal propagation and several other physical laws.

Figure 1.1. The exponential growth of microprocessor performance, known as Moore's law, shown over the past two decades.

The speed-of-light argument suggests that once the above limit has been reached, the only path to improved performance is the use of multiple processors. Of course, the same argument can be invoked to conclude that any parallel processor will also be limited by the speed at which the various processors can communicate with each other. However, because such communication does not have to occur for every low-level computation, the limit is less serious here. In fact, for many applications, a large number of computation steps can be performed between two successive communication steps, thus amortizing the communication overhead.

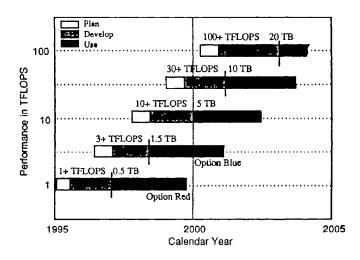

Here is another way to show the need for parallel processing. Figure 1.2 depicts the improvement in performance for the most advanced high-end supercomputers in the same 20-year period covered by Fig. 1.1. Two classes of computers have been included: (1) Cray-type pipelined vector supercomputers, represented by the lower straight line, and (2) massively parallel processors (MPPs) corresponding to the shorter upper lines [Bell92].

We see from Fig. 1.2 that the first class will reach the TFLOPS performance benchmark around the turn of the century. Even assuming that the performance of such machines will continue to improve at this rate beyond the year 2000, the next milestone, i.e., PFLOPS (peta FLOPS = 10<sup>15</sup> FLOPS) performance, will not be reached until the year 2015. With massively parallel computers, TFLOPS performance is already at hand, albeit at a relatively high cost. PFLOPS performance within this class should be achievable in the 2000–2005 time frame, again assuming continuation of the current trends. In fact, we already know of one serious roadblock to continued progress at this rate: Research in the area of massively parallel computing is not being funded at the levels it enjoyed in the 1980s.

But who needs supercomputers with TFLOPS or PFLOPS performance? Applications of state-of-the-art high-performance computers in military, space research, and climate modeling are conventional wisdom. Lesser known are applications in auto crash or engine combustion simulation, design of pharmaceuticals, design and evaluation of complex ICs, scientific visualization, and multimedia. In addition to these areas, whose current computational needs are met by existing supercomputers, there are unmet computational needs in

Figure 1.2. The exponential growth in supercomputer performance over the past two decades [Bell92].

aerodynamic simulation of an entire aircraft, modeling of global climate over decades, and investigating the atomic structures of advanced materials.

Let us consider a few specific applications, in the area of numerical simulation for validating scientific hypotheses or for developing behavioral models, where TFLOPS performance is required and PFLOPS performance would be highly desirable [Quin94].

To learn how the southern oceans transport heat to the South Pole, the following model has been developed at Oregon State University. The ocean is divided into 4096 regions E–W, 1024 regions N–S, and 12 layers in depth (50 M 3D cells). A single iteration of the model simulates ocean circulation for 10 minutes and involves about 30B floating-point operations. To carry out the simulation for 1 year, about 50,000 iterations are required. Simulation for 6 years would involve  $10^{16}$  floating-point operations.

In the field of fluid dynamics, the volume under study may be modeled by a  $10^3 \times 10^3 \times 10^3$  lattice, with about  $10^3$  floating-point operations needed per point over  $10^4$  time steps. This too translates to  $10^{16}$  floating-point operations.

As a final example, in Monte Carlo simulation of a nuclear reactor, about  $10^{11}$  particles must be tracked, as about 1 in  $10^8$  particles escape from a nuclear reactor and, for accuracy, we need at least  $10^3$  escapes in the simulation. With  $10^4$  floating-point operations needed per particle tracked, the total computation constitutes about  $10^{15}$  floating-point operations.

From the above, we see that  $10^{15}$ – $10^{16}$  floating-point operations are required for many applications. If we consider  $10^3$ – $10^4$  seconds a reasonable running time for such computa-

tions, the need for TFLOPS performance is evident. In fact, researchers have already begun working toward the next milestone of PFLOPS performance, which would be needed to run the above models with higher accuracy (e.g., 10 times finer subdivisions in each of three dimensions) or for longer durations (more steps).

The motivations for parallel processing can be summarized as follows:

- Higher speed, or solving problems faster. This is important when applications have "hard" or "soft" deadlines. For example, we have at most a few hours of computation time to do 24-hour weather forecasting or to produce timely tornado warnings.

- Higher throughput, or solving more instances of given problems. This is important when many similar tasks must be performed. For example, banks and airlines, among others, use transaction processing systems that handle large volumes of data.

- 3. Higher computational power, or solving larger problems. This would allow us to use very detailed, and thus more accurate, models or to carry out simulation runs for longer periods of time (e.g., 5-day, as opposed to 24-hour, weather forecasting).

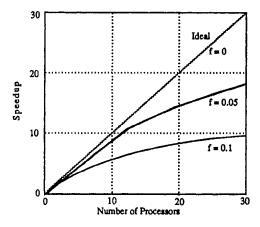

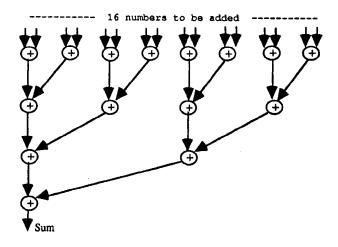

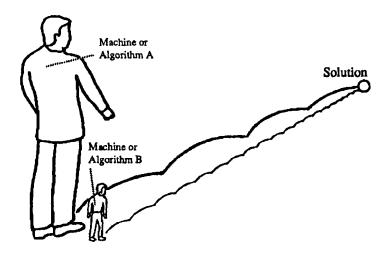

All three aspects above are captured by a figure-of-merit often used in connection with parallel processors: the computation *speed-up* factor with respect to a uniprocessor. The ultimate efficiency in parallel systems is to achieve a computation speed-up factor of *p* with *p* processors. Although in many cases this ideal cannot be achieved, *some* speed-up is generally possible. The actual gain in speed depends on the architecture used for the system and the algorithm run on it. Of course, for a task that is (virtually) impossible to perform on a single processor in view of its excessive running time, the computation speed-up factor can rightly be taken to be larger than *p* or even infinite. This situation, which is the analogue of several men moving a heavy piece of machinery or furniture in a few minutes, whereas one of them could not move it at all, is sometimes referred to as *parallel synergy*.

This book focuses on the interplay of *architectural* and *algorithmic* speed-up techniques. More specifically, the problem of algorithm design for *general-purpose* parallel systems and its "converse," the incorporation of architectural features to help improve algorithm efficiency and, in the extreme, the design of algorithm-based special-purpose parallel architectures, are considered.

### 1.2. A MOTIVATING EXAMPLE

A major issue in devising a parallel algorithm for a given problem is the way in which the computational load is divided between the multiple processors. The most efficient scheme often depends both on the problem and on the parallel machine's architecture. This section exposes some of the key issues in parallel processing through a simple example [Quin94].

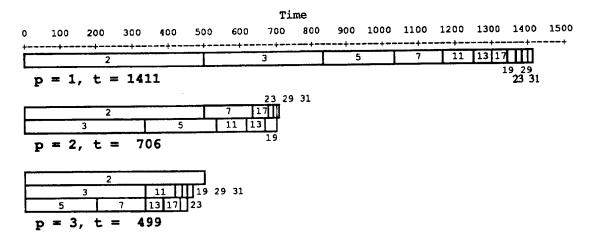

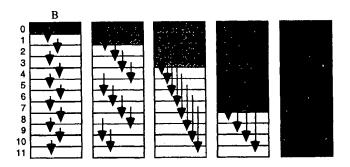

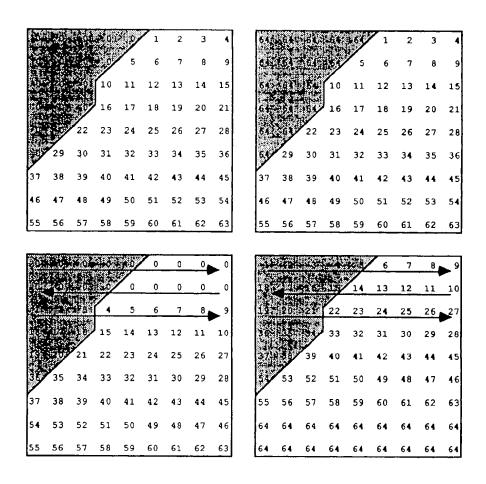

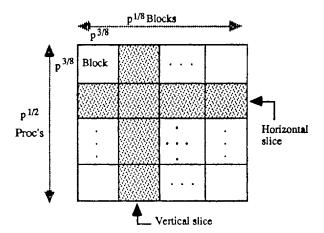

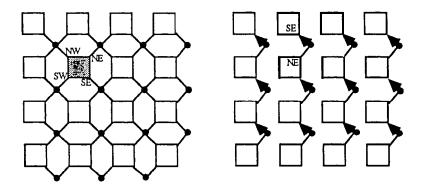

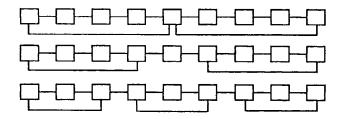

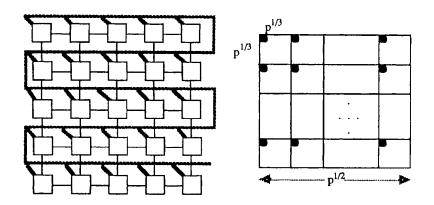

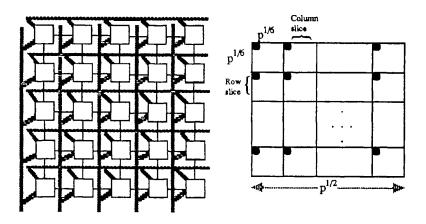

Consider the problem of constructing the list of all prime numbers in the interval [1, n] for a given integer n > 0. A simple algorithm that can be used for this computation is the sieve of Eratosthenes. Start with the list of numbers  $1, 2, 3, 4, \ldots, n$  represented as a "mark" bit-vector initialized to  $1000 \ldots 00$ . In each step, the next unmarked number m (associated with a 0 in element m of the mark bit-vector) is a prime. Find this element m and mark all multiples of m beginning with  $m^2$ . When  $m^2 > n$ , the computation stops and all unmarked elements are prime numbers. The computation steps for n = 30 are shown in Fig. 1.3.

| 2<br>π=2 | 3        | 4 | 5        | 6 | 7                     | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

|----------|----------|---|----------|---|-----------------------|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|          | 3<br>n=3 |   | 5        |   | 7                     |   | 9 |    | 11 |    | 13 |    | 15 |    | 17 |    | 19 |    | 21 |    | 23 |    | 25 |    | 27 |    | 29 |    |

| 2        | 3        |   | 5<br>n=5 |   | 7                     |   |   |    | 11 |    | 13 |    |    |    | 17 |    | 19 |    |    |    | 23 |    | 25 |    |    |    | 29 |    |

| 2        | 3        |   | 5        |   | 7<br>1 <del>-</del> 7 |   |   |    | 11 |    | 13 |    |    |    | 17 |    | 19 |    |    |    | 23 |    |    |    |    |    | 29 |    |

Figure 1.3. The sieve of Eratosthenes yielding a list of 10 primes for n = 30. Marked elements have been distinguished by erasure from the list.

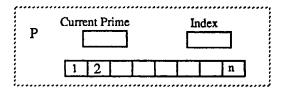

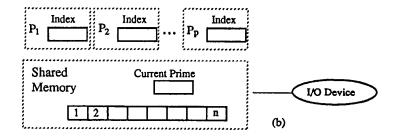

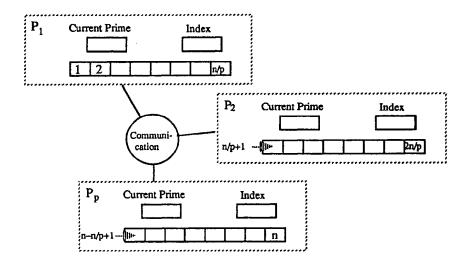

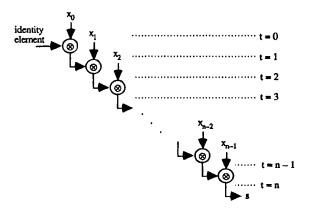

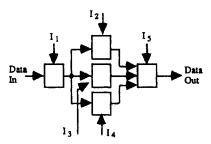

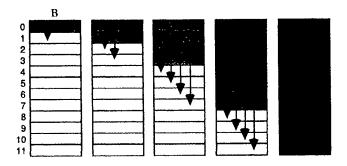

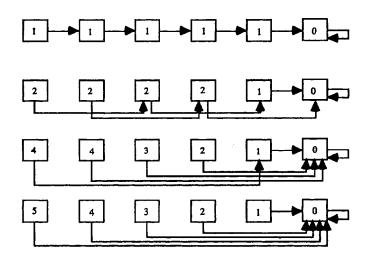

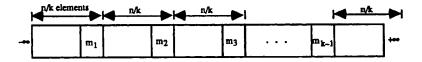

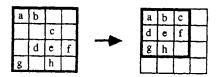

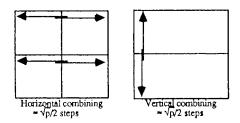

Figure 1.4. Schematic representation of single-processor solution for the sieve of Eratosthenes.

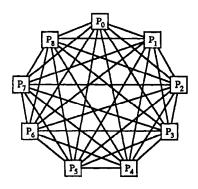

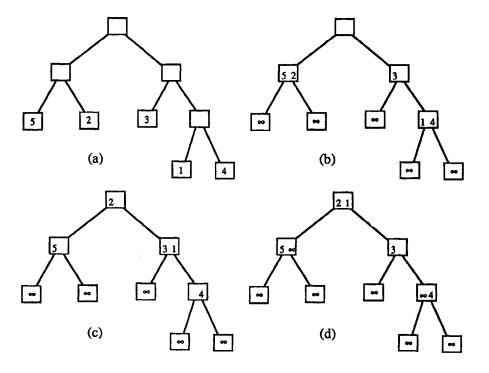

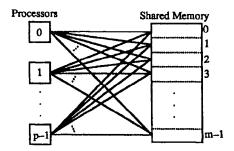

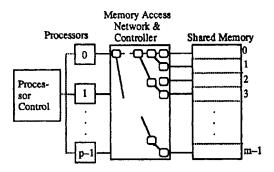

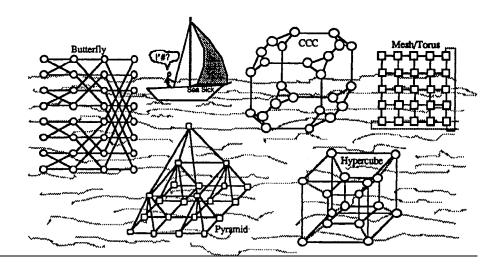

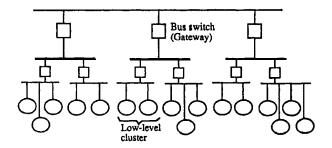

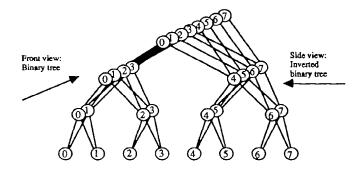

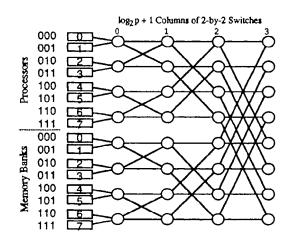

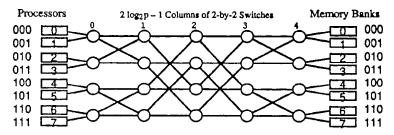

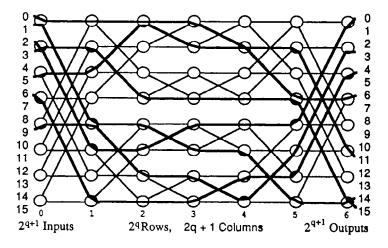

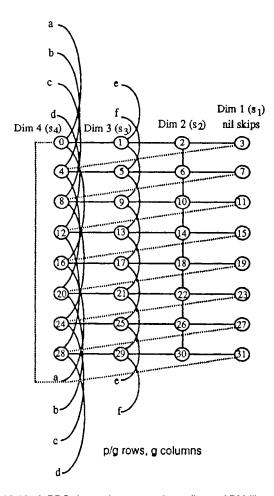

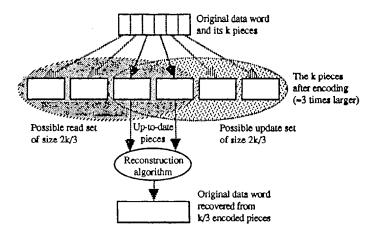

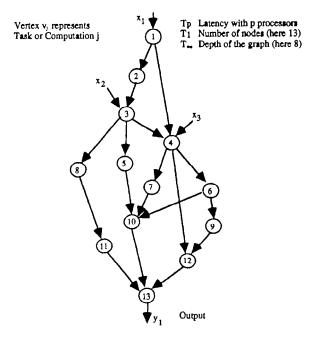

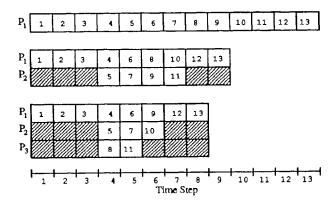

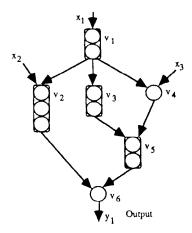

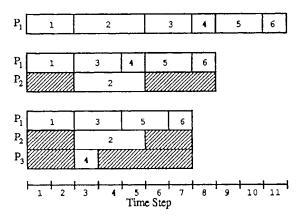

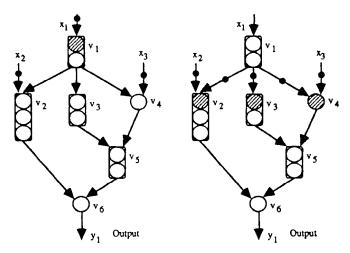

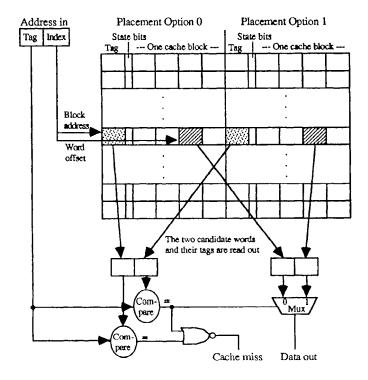

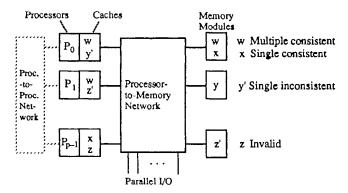

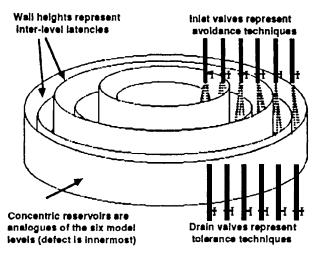

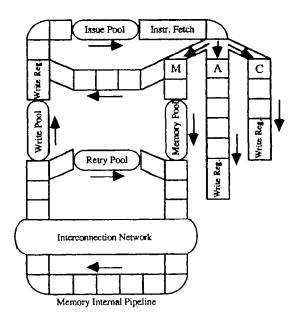

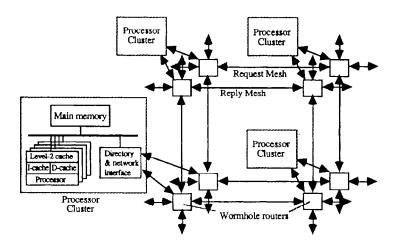

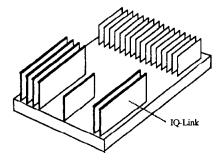

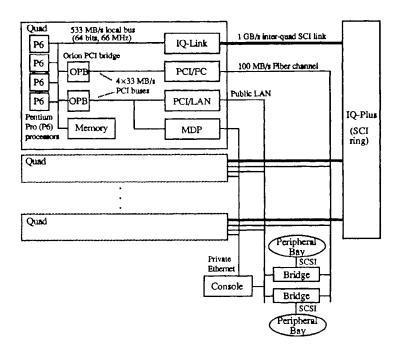

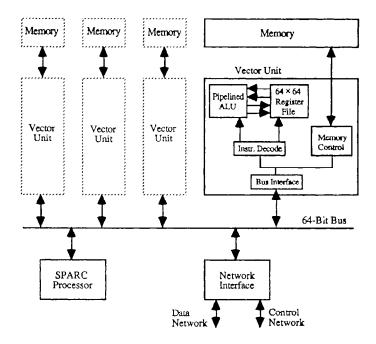

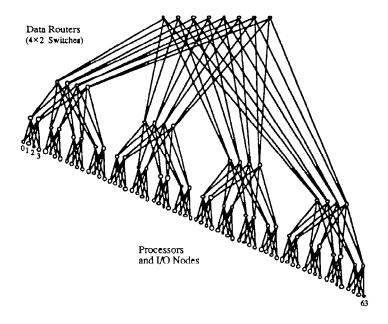

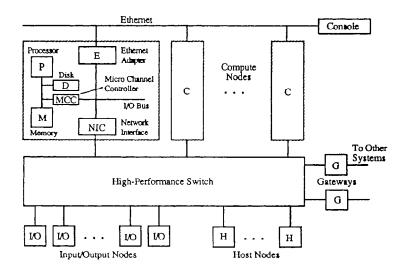

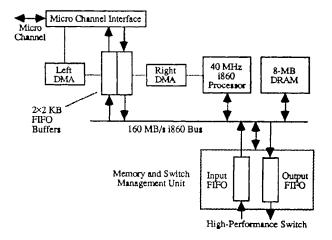

Figure 1.4 shows a single-processor implementation of the algorithm. The variable "current prime" is initialized to 2 and, in later stages, holds the latest prime number found. For each prime found, "index" is initialized to the square of this prime and is then incremented by the current prime in order to mark all of its multiples.